データセンターでの先端半導体パッケージング技術

2022年10月12日

Dr Yu-Han Chang

成長の原動力とユースケース

半導体は、私たちのデジタルライフを可能にする重要な部品です。その開発は大きな発展を遂げてきました。最初のシングルチッププロセッサであるIntel 4004のトランジスタ数がわずか2,250個であったのに対し、2022年現在の最先端のプロセッサのトランジスタ数は500億個を超えています。しかし、進歩には代償が伴います。先進的な製品を提供し続けながらコストを抑えることができるように、代替のソリューションを業界が求めなければならないレベルにまで開発費と生産コストの両方が上昇しています。加えて、デバイスを小型化し、異種部品をコンパクトに集積化し、配線密度を高めることが求められており、先端半導体パッケージングに対する注目度が高まっているのです。

本記事では、データセンター用途における先端半導体パッケージング技術の成長ドライバーを取り上げるほか、先端半導体パッケージング技術を活用した最先端の商用サーバー製品の例もいくつかご紹介します。 この内容は、IDTechExの最新市場調査レポート『先端半導体パッケージング 2023-2033年』からの引用です。本調査レポートはデータセンターに限らず、自動運転車、5G&6G、一般消費デバイス用途もカバーしています。

先端半導体パッケージング技術 - ハイパフォーマンスコンピューティングアプリケーション/データセンター向け次世代ICの重要な基盤

ハイパフォーマンスコンピューティング(HPC)アプリケーションやデータセンター向けにエネルギー効率の高いシステムを設計する際には、シリコンに関して、3つのトレンド(トランジスタの増加、メモリの増加、ロジックIC・メモリ間の配線の増加)を考慮しなければなりません。トランジスタを増やすには、チップ設計においてレチクルサイズの制限を超える必要がありますが、これは先端半導体パッケージングで対処できる領域を超えています。一方で、メモリを増やすこと(高帯域幅のオンチップメモリや、I/O数の増加によって実現可能)と、ロジックIC・メモリ間の配線を増やすことは、どちらも先端半導体パッケージング技術によって実現が可能です。

技術的進歩のほかに、コスト管理も依然として重要なポイントです。チップレット設計は、ベンダーがコストと性能のバランスを見いだすのを支援する方法として登場しました。チップレット設計とは、モジュール化によりプロセッサを作る方式です。チップレット設計では、最適なプロセスノードを用いてさまざまなダイ/チップを作ることができ、また、不要な部品への最先端のプロセスノード(高コスト)の使用を減らすことで、デバイスの総コストを抑えることが可能です。チップレット設計を後押しするもう1つの要因は、より多くのI/Oに対するニーズです。SerDes、PCIE、メモリI/OなどのI/Oダイを、2.5Dかそれに相当する半導体パッケージング技術を利用したプロセシングユニットと同じモジュールにパッケージングすると、システム内のI/O数を増やせるようになります。2.5Dの先端半導体パッケージングは、現在のところ、サブミクロン単位の配線を可能にする唯一の技術です。

最先端のユースケースと今後の開発動向

先端半導体パッケージング技術を使用している、あるいは実装する可能性のある最新の商用製品をいくつか見てみましょう。まずは、サーバー用CPUでの利用を例に取ってみましょう。現在のサーバー用CPUの大半はモノリシックSoC(システム・オン・チップ)をベースにしていますが、インテルは2021年に、次世代のサーバー用CPUとなるSapphire Rapids(サファイアラピッズ)が、EMIB(Embedded Multi-die Interconnect Bridge)によってつなぎ合わせた4チップモジュールをベースにしたものになると発表しました。EMIBは、インテルによる2.5Dの先端半導体パッケージングソリューションです。一方AMDは、キャッシュダイをプロセッサの上に直接載せる3Dの先端半導体パッケージング技術の力を利用することで、最新のサーバー用CPUとなるMilan-X(2022年3月発売の製品)の性能を高めています。

AMDは、この3Dパッケージングにより、通常の2Dパッケージングと比較して200倍以上となる配線密度が実現すると主張しています。業界第1位と第2位の大手サーバー用CPUサプライヤーが、どちらも自社の最新の先端技術製品で先端半導体パッケージング技術を利用していることもあり、この分野では先端半導体パッケージング技術の導入がますます進むと見られています。サーバー用CPU以外に、アクセラレータなど、データセンター内の他のコンポーネントにも先端半導体パッケージング技術がすでに採用されています。例えばNVIDIAでは、TSMCの2.5Dパッケージング技術であるCoWoS(チップ・オン・ウエハ・オン・サブストレート)を2016年からハイエンドのGPUアクセラレータに使用しています。

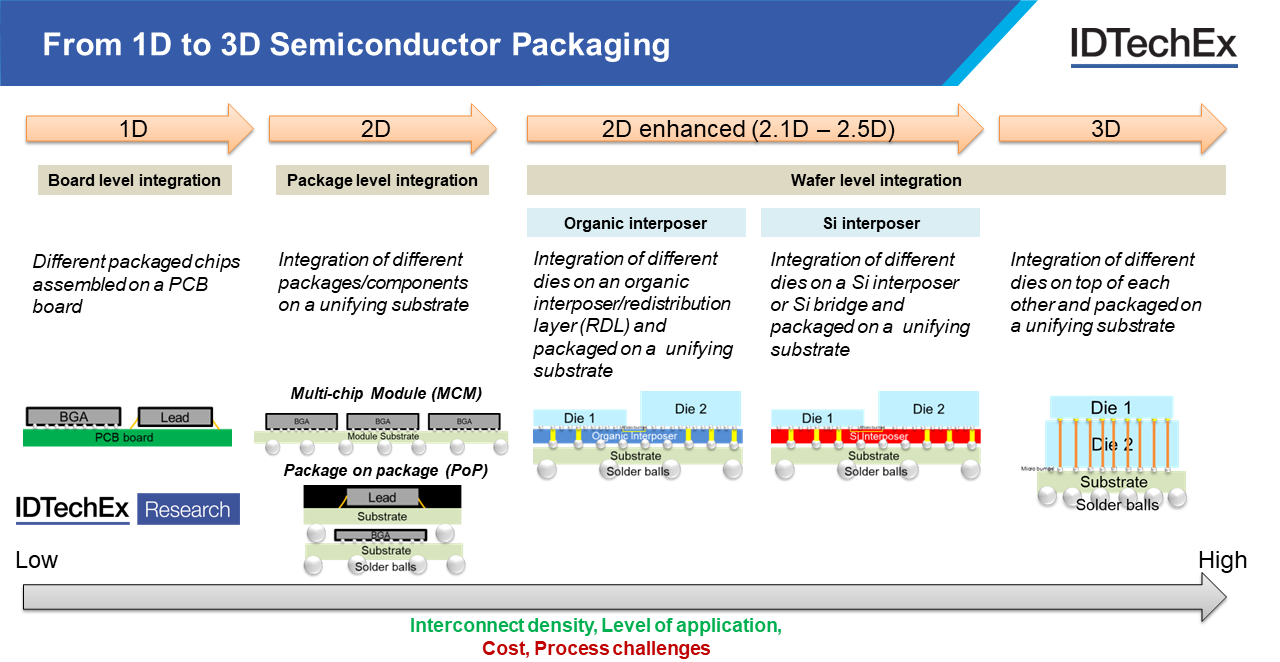

1Dから3Dまでの半導体パッケージング。 Source: IDTechEx - 『先端半導体パッケージング 2023-2033年』

ハイエンドの商用製品のいくつかでは2.5Dの先端半導体パッケージング技術がすでに使用されてはいますが、デバイスの性能をさらに向上させたり、追加のコンポーネントを収容できるようにパッケージサイズを拡大する開発の取り組みが数多く進められています。開発は、2.5Dを超える集積化へと進んでいきますが、最終的な目標は、多くのロジックICとメモリを物理的に重ね合わせる完全な3D集積化を実現することです。しかしその道は、決して一筋縄ではいきません。熱管理と製造において、まだ克服されていないいくつかの問題に直面しているのです。

最終的には、データセンター対する世界的なニーズが高まっていることを考えると、先端半導体パッケージング技術の進歩は、ハイパフォーマンスコンピューティングアプリケーション向けの次世代集積回路(IC)に不可欠であり、市場にかなりの影響を与えることになるでしょう。

IDTechExの調査レポート『先端半導体パッケージング 2023-2033年』は、先端半導体パッケージング技術の最新開発動向、キープレイヤー分析、市場展望を網羅しています。

主要項目

- シリコンIC業界の詳細な概要 - 技術ロードマップと関連プレイヤーの動向など

- 半導体IC業界におけるサプライチェーンとビジネスモデルの分析

- 各種半導体パッケージング技術の分析

- 主要企業の先端半導体パッケージング技術の詳細分析 - 当該企業の最先端技術と今後の研究開発など

- 先端半導体パッケージングの主要市場の詳細な概要。ハイパフォーマンスコンピューティング、自動運転車、5G、家電など

- 各種用途での先端半導体パッケージングの使用状況を示す多数のケーススタディ

- IDTechExの調査による、4つの主要市場(データセンター、自動運転車、5G、家電)における主な先端半導体パッケージング技術(2.5Dシリコン埋め込み、2.5シリコンインターポーザ、2.5D(超)高密度ファンアウト、3Dダイスタッキングなど)の市場拡張性

・アイディーテックエックス株式会社 (IDTechEx日本法人) が販売。

・IDTechExからの直接販売により、お客様へ各種メリットを提供。

・ご希望の方に、サンプルページ 送付。

・オンラインでの試読については、ご相談ください。

・その他、調査レポートに関する、質問、購入に関する問い合わせは、

下記担当まで。見積書、請求書も発行します。

IDTechExの調査レポートを購入すると、30分のアナリストタイムが提供されます。直接アナリストにレポートに関する質問が可能です。詳しくは、下記担当までお問い合わせください。

問合せ先

アイディーテックエックス株式会社

東京都千代田区丸の内1-6-2 新丸の内センタービル21階

担当:村越美和子 m.murakoshi@idtechex.com

電話 : 03-3216-7209

IDTechExは、調査、コンサルタント、サブスクリプションを通して、戦略的なビジネス上の意思決定をサポートし、先進技術からの収益を支援しています。IDTechExの調査およびコンサルティングの詳細については、IDTechExの日本法人、アイディーテックエックス株式会社まで、お問い合わせください。